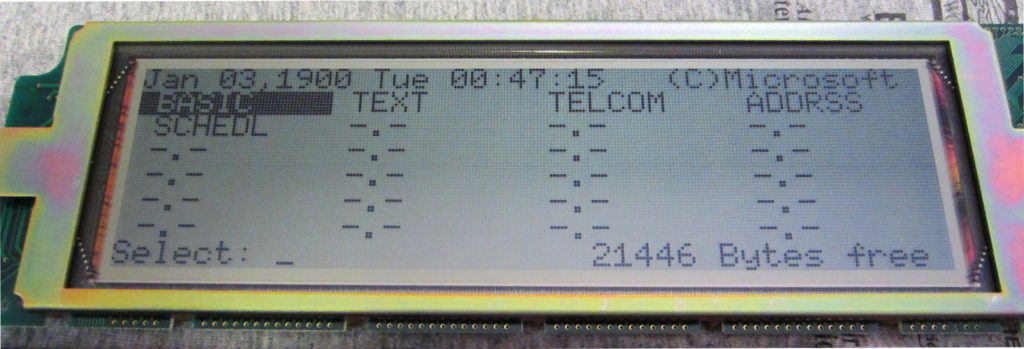

Here it is – taunting me!

That horrible number: 21446 Bytes free.

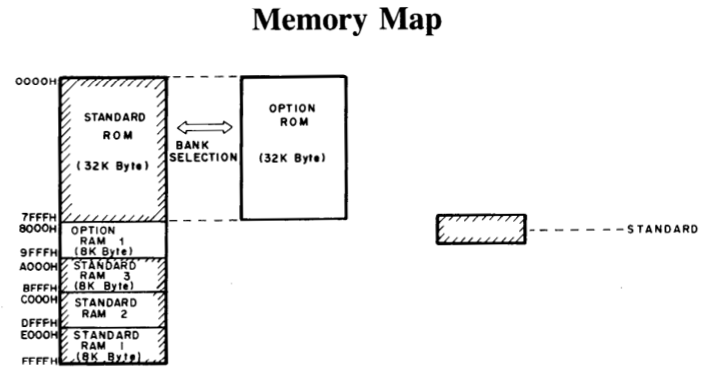

The Tandy 102 (and the Tandy 100 which came before it), like most vintage 8-bit systems, have a very simple memory map:

The Intel 8085 (an 8080 derivative) has a 16-bit address space, meaning it can address up to 64k of physical memory space. The system ROM occupies the top (lowest-address) 32k of memory space and the SRAMs occupy the bottom (highest-address) space. The space in the middle, between 8000 and 9FFF, is a little bit special: it’s reserved for the “Option RAM”. When the Tandy 10o was originally introduced, it shipped with only 8k of RAM installed, but had sockets for up to 24k of additional RAM. When the 102 was later released, being an upgrade of the 100, it shipped with 24k installed and left a single space open for an additional 8k of RAM: the “Option” RAM.

The Intel 8085 (an 8080 derivative) has a 16-bit address space, meaning it can address up to 64k of physical memory space. The system ROM occupies the top (lowest-address) 32k of memory space and the SRAMs occupy the bottom (highest-address) space. The space in the middle, between 8000 and 9FFF, is a little bit special: it’s reserved for the “Option RAM”. When the Tandy 10o was originally introduced, it shipped with only 8k of RAM installed, but had sockets for up to 24k of additional RAM. When the 102 was later released, being an upgrade of the 100, it shipped with 24k installed and left a single space open for an additional 8k of RAM: the “Option” RAM.

Together all four 8k RAM chips provide the full 32k of RAM from address FFFF to 8000. (Note that all of these RAM address numbers are given in hexadecimal notation.) However, as the Tandy 100 OS and various other memory structures occupy some memory even on a freshly booted system, a 32k Tandy 100 will show 29314 bytes free. The sad 21446 in the bottom-right corner of my unit is the max free space on a 24k system, meaning that it has lost 8k of RAM – a full quarter of its precious memory.

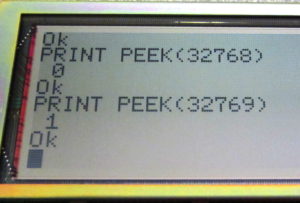

Could there be something wrong with the way the OS is detecting the memory configuration? Let’s use BASIC to query the memory space where the RAM chips live, starting at the “top” of memory space:

Right away, something isn’t right. What are the chances of two successive peeks at sequential addresses returning an incrementing series starting from zero? Lets keep poking. A quick BASIC program will read all addresses starting from 32768 (8000 hex):

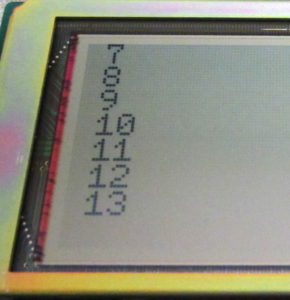

10 FOR I = 1 to 8000 20 PRINT PEEK (32768 + I) 30 NEXT I

The results aren’t pretty:

What in the world is going on?

The answer lies in the 80C85’s multiplexed data bus. The lower 8 bits (the least-significant bits) of the address bus are shared with the data bus. So, when accessing memory address 8000, the bottom 8 bits of the address bus are all zero. Then, after the address has been sent to the RAM chips and latched by the memory decoding circuit, the 80C05 reads the data lines; the RAM chip should have loaded an 8-bit data word onto these lines by now. However, if we have a faulty RAM chip, what’s left on the data bus is the lower byte of the address we read. Hence, as we increment the read address, the value we get from the PEEK also increments.

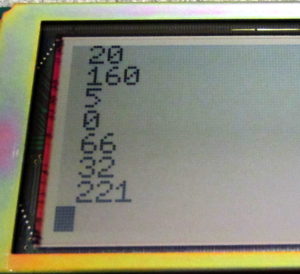

To confirm my suspicion, let’s try reading from a different RAM chip’s addresses:

Random values – exactly what we would expect when reading from a random address inside a working RAM chip. So, what’s wrong?

There are several potential causes:

No power?

I pulled up the datasheet for the 8464 SRAM. Vcc is reading 5v and ground is continuous with a known ground point. Strike 1

Bad trace?

A member on the Club 100 mailing list said that it’s not uncommon for Tandy 100/102 logic boards to develop bad traces. I checked continuity on the address/data bus and found it continuous with working chips. Strike 2

Bad decoding circuit?

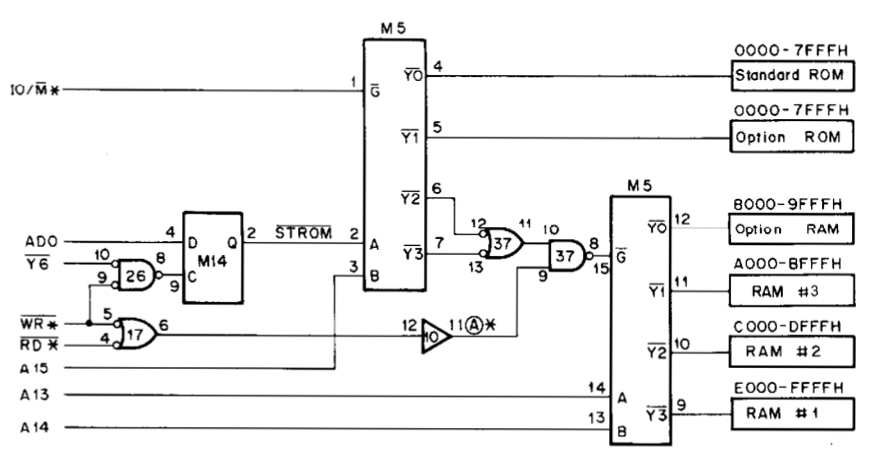

The Tandy 102 technical reference manuals (remember when you could get those?) lays out the memory decoding circuit.

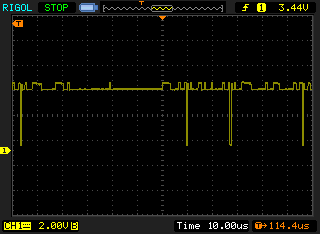

A multiplexer is used to turn top three bits of the address bus into individual chip enable signals for the 4 RAM chips. With this circuit, even though all four chips are receiving the same address on the bus, only one of them is active at any time. So, if I probe the chip enable lines, I should be able to see the decoder circuit activating the right chip at the right time. Probing RAM chip M7 (the one we saw giving the expected random bytes earlier), we see the enable line periodically going low (this is a low-active line, meaning the chip is enabled when the line goes to ground).

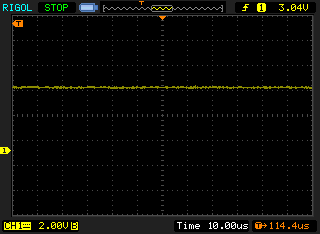

However, when probing M6 (the option RAM) chip enable, the line never goes low.

In fact, we don’t even see the small amount of digital noise present on M7’s chip enable line. I was hoping to find a bad trace here, but checking from the decoder mulitplexer to the M6 chip enable line shows zero ohms: an intact trace.

So, faced with these facts I must conclude that I have a dead RAM chip. Luckily, 8k x 8 (8 thousand “words” by 8 bits) SRAM chips are still readily available. A quick check on ebay brings up a 3-pack for $10 with free shipping. If only we’d had RAM prices like that in the ’80s!